#### Abstract

LOTOS (Language Of Temporal Ordering Specification) is one of the currently available Formal Description Techniques developed for the specification of OSI. It is based on the temporal relation among the interactions that constitute the externally observable behaviour of a system. On the other hand, PROMELA is a language used to describe both validation and specification models. The topic of this thesis is the design and implementation of a translator from LOTOS specifications into PROMELA validation models. LOTOS specifications are first syntactically and semantically checked and then they transformed into a network of extended finite state machines. The automata are then translated into PROMELA where they synchronise according to a multi rendezvous algorithm. Unfortunately, it is proved that due to the complexity of LOTOS multi synchronisation the number of states produced is too large to be analysed.

### Translating LOTOS Specifications into PROMELA

By

Nicholaos C. Petalidis

Submitted for the Degree of

Master of Philosophy

AT Heriot-Watt University

ON Completion of Research in the

Department of Computing and Electrical Engineering

October 1994.

This copy of the thesis has been supplied on the condition that anyone who consults it is understood to recognise that the copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author or the university (as may be appropriate).

I hereby declare that the work presented in this thesis was carried out by myself at Heriot-Watt University, Edinburgh, except where due acknowledgement is made, and has not been submitted for any other degree.

Nicholaos C. Petalidis (Candidate)

Dr. Peter J.B King (Supervisor)

Date

## Contents

| 1        | Intr | $\operatorname{oducti}$ | on                             | 1  |

|----------|------|-------------------------|--------------------------------|----|

|          | 1.1  | Prolog                  | ue                             | 1  |

|          | 1.2  | Organ                   | isation of the Thesis          | 1  |

|          | 1.3  | Overvi                  | iew of FDTs                    | 2  |

|          | 1.4  | Protoc                  | col verification               | 3  |

|          | 1.5  | A Lote                  | os to Promela Translator: Why? | 5  |

|          | 1.6  | Relate                  | d Work                         | 6  |

|          | 1.7  | Epilog                  | ue                             | 9  |

| <b>2</b> | An   | overvi                  | ew of LOTOS                    | 10 |

|          | 2.1  | Prolog                  | ue                             | 10 |

|          | 2.2  | Genera                  | al Principles                  | 11 |

|          | 2.3  | Basic 1                 | Lotos                          | 12 |

|          |      | 2.3.1                   | Inaction: stop                 | 12 |

|          |      | 2.3.2                   | Action prefix                  | 12 |

|          |      | 2.3.3                   | Choice                         | 13 |

|          |      | 2.3.4                   | Parallel Composition           | 13 |

|          |      | 2.3.5                   | Hiding                         | 14 |

|          |      | 2.3.6                   | Successful termination: exit   | 14 |

|          |      | 2.3.7                   | Enabling                       | 14 |

|          |      | 2.3.8                   | Disabling                      | 15 |

|          |      | 2.3.9                   | Process Instantiation          | 15 |

|   | 2.4 | Data ' | Types                                     | 15 |

|---|-----|--------|-------------------------------------------|----|

|   |     | 2.4.1  | Signature                                 | 15 |

|   |     | 2.4.2  | Equations                                 | 16 |

|   |     | 2.4.3  | Extension                                 | 17 |

|   |     | 2.4.4  | Combining                                 | 17 |

|   |     | 2.4.5  | Renaming                                  | 17 |

|   |     | 2.4.6  | Parameterised Data Types                  | 18 |

|   | 2.5 | Full L | OTOS                                      | 18 |

|   |     | 2.5.1  | Action prefix                             | 19 |

|   |     | 2.5.2  | Parallel Composition in Full LOTOS        | 20 |

|   |     | 2.5.3  | Successful termination with parameters    | 20 |

|   |     | 2.5.4  | Guarded behaviour                         | 21 |

|   |     | 2.5.5  | Sequential composition with value passing | 21 |

|   |     | 2.5.6  | Generalised choice                        | 21 |

|   |     | 2.5.7  | Parametric processes                      | 22 |

|   |     | 2.5.8  | Local Definitions                         | 22 |

|   |     | 2.5.9  | Par Expression                            | 23 |

|   | 2.6 | Epilog | gue                                       | 23 |

| 3 | An  | overvi | ew of PROMELA                             | 24 |

|   | 3.1 | Prolog | gue                                       | 24 |

|   | 3.2 | Stater | ments                                     | 24 |

|   | 3.3 | Variab | oles, Data types                          | 24 |

|   | 3.4 | Procee | dures                                     | 25 |

|   |     | 3.4.1  | The initial process                       | 25 |

|   |     | 3.4.2  | Atomic sequences                          | 26 |

|   | 3.5 | Messa  | ge channels                               | 26 |

|   | 3.6 | Contro | ol Flow                                   | 28 |

|   | 3.7 | Timec  | outs                                      | 29 |

|   | 3.8 | Correc | ctness Criteria                           | 29 |

|   |      | 3.8.1 Assertions                 |      |      |    | <br> |  |      | <br> | 30         |

|---|------|----------------------------------|------|------|----|------|--|------|------|------------|

|   |      | 3.8.2 Deadlocks                  |      |      |    | <br> |  | <br> | <br> | 30         |

|   |      | 3.8.3 Non-progress cycles        |      |      |    | <br> |  | <br> | <br> | 30         |

|   |      | 3.8.4 Livelocks                  |      |      |    | <br> |  | <br> | <br> | 30         |

|   |      | 3.8.5 Temporal claims            |      |      |    | <br> |  |      | <br> | 31         |

|   | 3.9  | A simple example                 |      |      |    | <br> |  | <br> | <br> | 32         |

|   | 3.10 | Epilogue                         |      |      |    | <br> |  |      | <br> | 35         |

| 4 | An   | overview of SPIN                 |      |      |    |      |  |      |      | 36         |

|   | 4.1  | Prologue                         |      |      |    | <br> |  | <br> | <br> | 36         |

|   | 4.2  | Validation algorithms            |      |      |    | <br> |  | <br> | <br> | 36         |

|   |      | 4.2.1 Full State Search Meth     | od   |      |    | <br> |  | <br> | <br> | 37         |

|   |      | 4.2.2 Controlled partial search  | ch . |      |    | <br> |  |      | <br> | 38         |

|   |      | 4.2.3 Random simulation          |      |      |    | <br> |  | <br> | <br> | 39         |

|   | 4.3  | Other algorithms                 |      |      |    | <br> |  |      | <br> | 39         |

|   | 4.4  | Using the validator              |      |      |    | <br> |  |      | <br> | 41         |

|   | 4.5  | Validation Techniques            |      |      |    | <br> |  |      | <br> | 42         |

|   | 4.6  | Epilogue                         |      |      |    | <br> |  | <br> | <br> | 43         |

| 5 | Trai | nslation of basic LOTOS          |      |      |    |      |  |      |      | <b>4</b> 4 |

|   | 5.1  | Prologue                         |      |      |    | <br> |  |      | <br> | 44         |

|   | 5.2  | Lexical and Syntax Analysis .    |      |      |    | <br> |  | <br> | <br> | 45         |

|   | 5.3  | Creation of Abstract Syntax T    | rees |      |    | <br> |  | <br> | <br> | 48         |

|   | 5.4  | Identification of non regular ex | xpre | ssic | ns | <br> |  | <br> | <br> | 51         |

|   | 5.5  | XFSM creation                    |      |      |    | <br> |  | <br> | <br> | 59         |

|   |      | 5.5.1 State Machines             |      |      |    | <br> |  |      | <br> | 60         |

|   |      | 5.5.2 Inaction: stop             |      |      |    | <br> |  | <br> | <br> | 63         |

|   |      | 5.5.3 Action prefix              |      |      |    | <br> |  | <br> | <br> | 64         |

|   |      | 5.5.4 Choice                     |      |      |    | <br> |  | <br> | <br> | 64         |

|   |      | 5.5.5 Hiding                     |      |      |    | <br> |  | <br> | <br> | 65         |

|   |     | 5.5.6 Parallel Composition          | 67  |

|---|-----|-------------------------------------|-----|

|   |     | 5.5.7 Enabling                      | 73  |

|   |     | 5.5.8 Disabling                     | 75  |

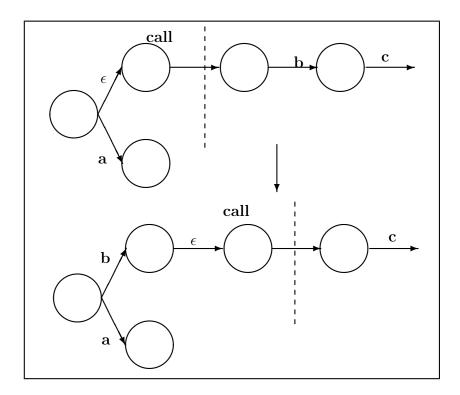

|   |     | 5.5.9 Process Instantiation         | 77  |

|   | 5.6 | Optimisation of XFSMs               | 80  |

|   | 5.7 | Epilogue                            | 85  |

| 6 | XFS | SM Synchronisation                  | 86  |

|   | 6.1 | Prologue                            | 86  |

|   | 6.2 | The multi-way Rendezvous            | 86  |

|   |     | 6.2.1 The execution model           | 87  |

|   |     | 6.2.2 The Algorithm                 | 89  |

|   | 6.3 | Implementation of callP             | 95  |

|   | 6.4 | The callD command                   | 96  |

|   | 6.5 | The callE command                   | 97  |

|   | 6.6 | Epilogue                            | 97  |

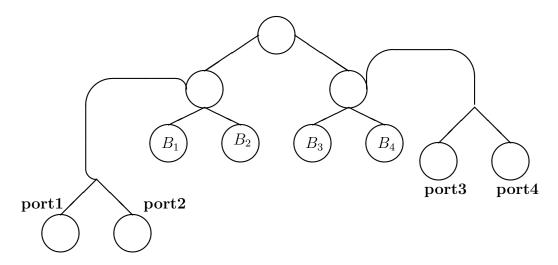

| 7 | A d | ifferent algorithm and a discussion | 99  |

|   | 7.1 | Prologue                            | 99  |

|   | 7.2 | The execution model                 | 99  |

|   | 7.3 | Description of the Algorithm        | 100 |

|   |     | 7.3.1 Assumptions and definitions   | 100 |

|   |     | 7.3.2 The algorithm                 | 101 |

|   | 7.4 | Discussion of the algorithm         | 103 |

|   | 7.5 | Epilogue                            | 106 |

| 8 | The | data part of LOTOS                  | .07 |

|   | 8.1 | Prologue                            | 107 |

|   | 8.2 | Translation of the data part        | 107 |

|   | 8.3 | The data part in PROMELA            | 110 |

|   | Q / | Epilogue 1                          | 111 |

| 9                | Con  | onclusion               |     |  |  |  |  |  |

|------------------|------|-------------------------|-----|--|--|--|--|--|

|                  | 9.1  | Prologue                | 113 |  |  |  |  |  |

|                  | 9.2  | State of the Translator | 113 |  |  |  |  |  |

|                  | 9.3  | Further Work            | 114 |  |  |  |  |  |

|                  | 9.4  | Epilogue                | 115 |  |  |  |  |  |

| $\mathbf{A}$     | Basi | ic LOTOS                | 116 |  |  |  |  |  |

|                  | A.1  | Prologue                | 116 |  |  |  |  |  |

|                  | A.2  | The grammar             | 116 |  |  |  |  |  |

| В                | The  | callP command           | 123 |  |  |  |  |  |

|                  | B.1  | Prologue                | 123 |  |  |  |  |  |

|                  | B.2  | The code                | 123 |  |  |  |  |  |

| $\mathbf{C}$     | The  | callD command           | 128 |  |  |  |  |  |

|                  | C.1  | Prologue                | 128 |  |  |  |  |  |

|                  | C.2  | The code                | 128 |  |  |  |  |  |

| D                | The  | callE command           | 132 |  |  |  |  |  |

|                  | D.1  | Prologue                | 132 |  |  |  |  |  |

|                  | D.2  | The code                | 132 |  |  |  |  |  |

| Bibliography 135 |      |                         |     |  |  |  |  |  |

# List of Figures

| 1  | Processes interacting with each other           | 11  |

|----|-------------------------------------------------|-----|

| 2  | Example of a signature                          | 16  |

| 3  | Actions in full LOTOS                           | 20  |

| 4  | Path to implement the translator                | 45  |

| 5  | Structure of the symbol table                   | 48  |

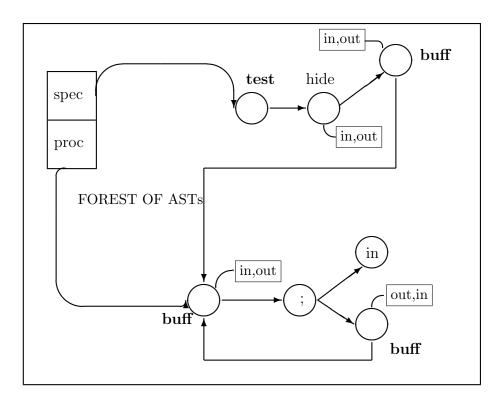

| 6  | An example of a forest of abstract syntax trees | 50  |

| 7  | Detection of non regular expressions            | 53  |

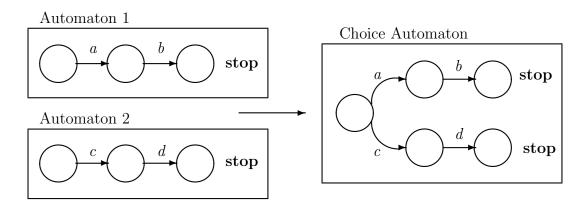

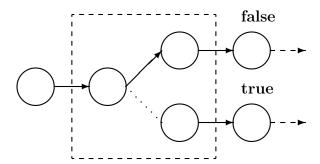

| 8  | An automaton for a choice expression            | 65  |

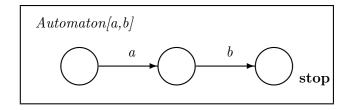

| 9  | An automaton without declarations               | 66  |

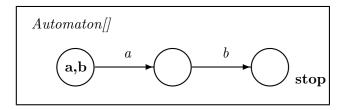

| 10 | An automaton with declarations                  | 66  |

| 11 | Transforming a choice expression                | 72  |

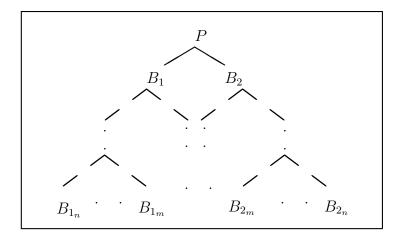

| 12 | Process decomposition of Lotos specifications   | 88  |

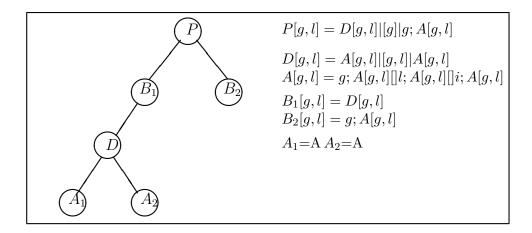

| 13 | A specification and the resulted execution tree | 93  |

| 14 | Instance of a process tree                      | 104 |

| 15 | Incorporating a data compiler                   | 110 |

## Acknowledgements

I am most grateful to my supervisor Dr. Peter J.B. King for all the guidance and valuable advice that he has given to me throughout my graduate studies.

I also like to thank my friends A. Kaloxylos and C. Farmakis for their help.

Special thanks to my parents Christos and Irene that supported me throughout my undergraduate and graduate studies.

## Chapter 1

## Introduction

### 1.1 Prologue

The evolution of computer networks gave rise to the problem of specifying and verifying "correct" protocols for the error free communication between computer systems.

The International Organisation for Standardisation (ISO) in an attempt to find solutions to this problem has worked towards the creation of a set of formal languages that enable the unambiguous specification of protocols and services.

On the other hand, a protocol must not only be "unambiguously" specified, but it must be guaranteed to work under all possible circumstances. Various techniques for the analysis of the behaviour of protocols have been proposed and implemented and a number of different *validators* are now in existence.

### 1.2 Organisation of the Thesis

In the following sections, a closer look at formal description techniques (FDTs) will be made. A discussion on the notion of verification and its importance in the development of protocols is presented and finally, an outline of the motives for this project as well as a review of projects in related areas is made.

Chapters 2, 3, 4 give an overview of the LOTOS specification language, the PROMELA verification language and describe the features of the SPIN validator.

In Chapter 5 a detailed description of the translator is made. The process of producing extended finite state machines from basic LOTOS specifications is explained in detail. Chapter 6 explains the protocol followed for the synchronisation of the finite machines.

A discussion on the final result is made in Chapter 7. The difficulties of obtaining an extended analyser for basic LOTOS specifications are presented. We also present a different rendezvous algorithm, that uses a minimum number of message transfers. Unfortunately, it also fails to keep the state space produced for the LOTOS specifications small.

Chapter 8 explains why the data part has not been incorporated in the translator.

In the last chapter, Chapter 9, the reader can find guidelines and ideas for extending this work.

### 1.3 Overview of FDTs

Formal Description Techniques (FDTs) are methods of defining the behaviour of an (information processing) system in a language with a formal syntax and semantics, instead of a natural language [ISO89a].

FDTs give us the ability to specify systems in a consistent way avoiding any possible misunderstanding that may lead to incompatible implementations. Moreover, FDTs allow for the analysis of protocols to be made on a mathematical basis.

The three FDTs in common use today are LOTOS [ISO89a], ESTELLE [ISO89b] and SDL [CCI89]. The first two techniques, (LOTOS and ESTELLE) were developed particularly for the specification of OSI protocols but nowadays they are used anywhere where the specification of a parallel protocol is needed. The process parts of SDL and ESTELLE are based on Extended Finite State Machines

(EFSM), a model that was quite famous in protocol specification methods from the early years. Although EFSM-based languages are easily implemented they lack of the abstractness needed to write machine - independent protocols.

LOTOS came to fill this gap. Based on a whole different philosophy it allows one to produce specifications that are not dependent on a particular system. Unfortunately, it is due to this abstractness that LOTOS is the hardest to implement of the formal description techniques.

The data parts of both LOTOS and SDL are based on abstract data types and more precisely on the language ACT-ONE [EM85]. This is something that gave both languages extra strength. Programmers can define their own data and operations and they can generalise their functions wherever possible. On the other hand, this is proving to be cumbersome for the people trying to derive running prototypes from these languages. The more abstract a language is, the more difficult it is to derive a concrete implementation from it.

Finally, the data part of ESTELLE is more concrete, having a lot similarities with the PASCAL programming language.

Apart from the three description techniques mentioned above a number of different languages exist for the formal specification of systems, although they are not considered to be FDTs. Examples of such languages are the specification languages Z [MS92], VHDL [Per94], and RAISE [Geo91].

### 1.4 Protocol verification

Verification became an important part of protocol design as computer systems became faster and more complex. The basic idea behind verification is that a method is needed to ensure that a protocol does not contain any logic contradictions and it does what it is supposed to do. Although the last sentence may seem a little bit naive, (why should anyone write a protocol that does not do the job it was created for) it must be realised that when we describe complex systems it is very difficult to take under consideration all the possible states they may fall in.

Apart from that, the term *validation of protocols* is also used in a broader sense and its interpretation depends on the user's interests and objectives. Thus, the objective could be to verify that a specified service satisfies the user requirements. Another objective could be to prove that a given implementation of a protocol correctly conforms to its specification [Peh90].

In this context the term is used to refer to some kind of proof that a protocol satisfies a given set of criteria, or in other words that the protocol actually provides the service we want.

Thus, to verify a protocol we need two things: A specification of the protocol itself and a specification of the properties the protocol must respect.

So, in order for the verification procedure to understand and analyse a specification, both the protocol and its properties have to be written in some predefined notation.

There is a number of different methods that can be used for the specification of protocols and their properties. Common approaches are the use of state machines, petri nets or state-charts. Properties are usually specified in terms of assertions associated with a transition system [Peh90].

Furthermore, the verification procedure must rely on some predefined algorithms for proving that the protocol satisfies its properties [GG93]. These algorithms either try to exhaustively explore every possible execution sequence of the protocol (reachability analysis) or they trace only those sequences that are more likely to produce an error (state space explosion). In Chapter 4 a detailed description of these techniques can be found.

In addition, it is possible to prove that the protocol under consideration is actually equivalent to another one that it is either simpler or known to be correct. Similarly a protocol can be validated if its specification is proved to be equivalent to the specification of the service it should provide. In general, two specifications are said to be equivalent when they can be used interchangeably. There are a

number of different equivalences in use today. Some of them require the specifications to be almost identical while others have more relaxed laws. The reader can find more information on equivalence relations in references [MS88, Hen88].

To help the process of verification a number of tools have been developed that aim either to fully automate the validation process or to help in cases where a fully automated method can not be followed.

Examples of such tools [JT93] are state space analysers which try to follow every possible execution sequence of a specification and simulators which trace a particular execution sequence. Other tools can be used to prove the equivalence of two specifications (equivalence checkers) or to derive test cases that can be used to check if an implementation conforms to its specification (test generators).

### 1.5 A Lotos to Promela Translator: Why?

The previous discussion made clear that in order to apply an automated method (e.g. reachability analysis) for verifying a protocol we need to express the protocol and its properties into a form acceptable by some validation tool.

These days the number of protocols expressed in the specification language LOTOS is continually increasing. However, LOTOS is not intended for validation purposes and this means that it is necessary to find a way for verifying LOTOS protocols. One method, of course, is to write validation tools that can directly understand and manipulate LOTOS inputs. Projects that are oriented towards this direction are presented in the next section.

Another method is to use existing tools and translate LOTOS specifications in a form that these tools understand. This is the method followed here.

The validation tool used is SPIN<sup>1</sup>. SPIN is a very powerful reachability analysis tool. It uses the most up-to-date validation algorithms and it allows for reachability analysis, state space explosion and random simulation. Moreover, its

<sup>&</sup>lt;sup>1</sup>As of March '95 a new version of SPIN(v. 2.0) is available. However, the version of SPIN used in this project is an earlier one (v. 1.5.14).

input language, PROMELA, can be used to express any correctness criteria and assertions that the user feels are necessary to be proven.

A tool that translates LOTOS specifications into PROMELA will provide protocol designers with the flexibility and abstractness they need for their specifications (using LOTOS) enhanced with the guarantee of the protocol's correctness (using SPIN).

In addition, a translator of LOTOS combined with the analogous translator of ESTELLE [Kal95] can be used to compare or even combine specifications written in these languages.

#### 1.6 Related Work

Several attempts have been made to obtain running implementations from LOTOS specifications. In this section a description of the compilers and simulators for LOTOS currently available will be made.

#### • The SEDOS project

The SEDOS project, begun in 1984 and finished in 1987, had the primary aim of further developing LOTOS and ESTELLE formal description techniques. SEDOS produced a number of tools and methods for simulating, verifying and testing LOTOS specifications [vE89, Tre89]. A great deal of the work currently going on in LOTOS is based on the results of the SEDOS project.

#### • TOPO

The Technical University of Madrid has created TOPO, a set of tools that allows the compilation of both the data type and control part of LOTOS and the derivation of code written either in C or in ADA. For the translation of the data part a rewrite system is generated while a network of finite state machines synchronised by a central controller comes to serve as a model for

the control part. The tool-set also enables the use of executable comments that try to minimise the abstractness of a specification. TOPO covers full LOTOS [AMnDSA93, Tur93].

#### • LOTOS interpreter of the University of Ottawa

A number of research projects concerning LOTOS have been carried out by the University of Ottawa. The main tool created there is an interpreter consisting of two parts: one that handles the data types of LOTOS (the SVELDA interpreter) and one that handles the control part of the language (the ISLA interpreter). The tool validates and evaluates value expressions and produces prototypes from LOTOS specifications and it is written in the PROLOG programming language [GL93, Tur93].

#### • CADP (Caesar/Aldebaran Distribution Package)

The CADP tool-box is dedicated to the efficient compilation, simulation, formal verification, and testing of descriptions of LOTOS specifications. The tool-box contains several closely interconnected components: ALDEBARAN, CAESAR, CAESAR.ADT, and OPEN/CAESAR.

#### ALDEBARAN

ALDEBARAN is a tool for verifying communicating systems, represented by labelled transition systems (LTS), i.e. finite state machines, the transitions of which are labelled by action names.

#### CAESAR

CAESAR is a compiler which translates LOTOS descriptions into LTSs. It interfaces a number of verification tools for LTSs and temporal logic evaluators.

#### CAESAR.ADT

CAESAR.ADT is a compiler that translates the data part of LOTOS specifications into libraries of C types and functions.

#### OPEN/CAESAR

OPEN/CAESAR is an extensible environment based upon CAESAR and CAESAR.ADT. It allows user-defined programs for simulation, execution, verification (partial, on-the-fly, etc.), and test generation to be developed in a simple and modular way.

The tool accepts full LOTOS with the exception of specifications that contain dynamically created processes [CFGM<sup>+</sup>92, Tur93].

#### • LOLA

LOLA is a transformational and state exploration tool used for testing, simulation and debugging purposes. LOLA can produce finite state machines, extended finite state machines or behaviour trees. It has options for simulating a LOTOS specification or evaluating data expressions. LOLA covers full LOTOS [QPF90, Tur93].

#### • SMILE

SMILE is a symbolic evaluation tool for LOTOS which can analyse the data part and produce a rewrite system. It has functions for the execution and debugging of a specification and can produce extended finite state machines that are equivalent (strong bisimulation equivalence) with the specification. SMILE covers full LOTOS but it can only execute finite specifications [EW93, Tur93].

#### • Other tools

A number of other tools exist, that either translate LOTOS sources into another language, such as the LOTOS to PARLOG translator [Gil88] or produce executable code not only for LOTOS but for other formal description techniques as well ([BBD<sup>+</sup>92]).

Nowadays, research efforts are directed towards the translation of LOTOS specifications into a network of extended finite state machines that co-operate according to some multi-rendezvous algorithm([Kar92, VSC90]). Labelled transition systems have been proven to produce inefficient implementations as they are not able to handle non regular processes correctly.

Finally, it should be mentioned that efforts are made to formally define and standardise extended versions of LOTOS that can handle real time [LLdF<sup>+</sup>94]. Time extended LOTOS is extremely useful for applications containing real time, such as video, audio and industrial applications and the production of tools that can handle the extended versions will be of crucial importance.

### 1.7 Epilogue

In this chapter the concept of specification and verification of protocols was introduced. A presentation of the three formal languages in use today was made and the need for a tool that will translate specifications written in these languages into another format was explained. The chapter closed with a review of projects and tools related with this subject. A detailed description of this project can be found in the subsequent chapters.

## Chapter 2

## An overview of LOTOS

### 2.1 Prologue

LOTOS (Language Of Temporal Ordering Specification) is a formal description technique standardised for the OSI (Open Systems Interconnection) services and protocols. LOTOS specifications describe distributed systems by defining the temporal relations among the interactions that represent the system's externally observable behaviour [BB87].

LOTOS specifications consist of two components:

- A control component based on Milner's Calculus of Communicating Systems (CCS [Mil80, Mil89]) and Hoare's Communication Sequential Processes (CSP [Hoa85]), which deals with the description of process behaviours and interactions, and

- 2. A data component based on the formal theory of algebraic abstract types ACT-ONE [EM85], that describes the data structures and value expressions.

Due to the mutual independence of the two components of LOTOS it is possible to write specifications which do not make use of data values; they constitute the subset of LOTOS called basic (or pure) LOTOS. Actually, this part is the CCS/CSP component of LOTOS.

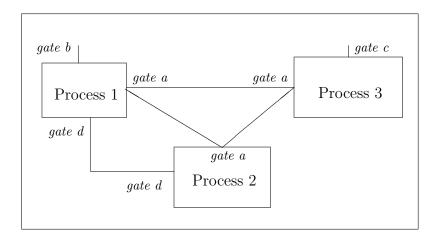

Figure 1: Processes interacting with each other

### 2.2 General Principles

In LOTOS a system is specified as a process possibly made up of several interacting subprocesses, each of which is a process too and may itself be divided into subprocesses. We can also assume that the observer of the system is a process ready to observe any observable action.

Interaction among processes takes place at communication points called gates. Thus, every process is characterised by a number of gates. Every observable action in which a process can participate is expressed by an action denotation composed of a gate identifier (where the action may occur) and, optionally, a data exchange part. Actions in LOTOS are atomic, i.e. it is considered that they do not consume time. When a process is ready for an interaction at some gate we say that it is ready to offer an observable action at that gate.

In general we can think of processes in LOTOS as being black boxes communicating with each other and the environment by a number of predefined gates, like in Figure 1. There we have three processes that interact with the environment (via gates b, c) and with each other (via gate d or gate a).

### 2.3 Basic Lotos

The control component of LOTOS deals with the description of process behaviours and interactions.

The syntax of a process definition looks like:

A behaviour-expression relates the order in which events may occur and is built up by applying an operator to other behaviour expressions. The precedence of each operator is:

action prefix > choice > parallel composition > disabling > enabling > hiding

The semantics of each of the operators are described below:

### 2.3.1 Inaction: stop

This operator indicates the completely inactive process. It does not offer anything to the environment and it does not have any internal actions to perform. **Stop** can be thought as being equivalent to *deadlock* if no other possibilities exist.

### 2.3.2 Action prefix

Syntax: i;B or g;B

where B is a behaviour expression, g a name of a gate and  $\mathbf{i}$  a special gate-name that denotes the unobservable internal action.

CHAPTER 2. AN OVERVIEW OF LOTOS

13

This operator expresses sequential composition of actions. In general it means that an event must occur at the specified gate in order for the process to proceed. As soon as the event occurs, the process behaves according to expression B.

#### 2.3.3 Choice

Syntax:  $B_1[]B_2$

The choice operator offers a choice between two behaviour expressions  $B_1$ ,  $B_2$ . The choice is usually resolved by the environment. If both choices are equally possible the result is a non-deterministic one. It should be mentioned here that once an action is chosen from one of the components, the other component disappears from the resulting expression.

This means, that if we had an expression:

and the first action chosen was a then the only possible action afterwards would be b. The right part of the expression was dropped as soon as the selection was made.

### 2.3.4 Parallel Composition

Syntax:  $B_1|[list\ of\ gates]|B_2$

This operator denotes the case where  $B_1$  and  $B_2$  are executed independently but synchronising at the gates mentioned in the list 'list of gates'.

If the 'list of gates' is the empty set then the two processes will be executed in an interleaved way. We denote this special case by using the ||| operator. If, on the other hand, we want to achieve full synchronisation between two processes, i.e both of them must synchronise in every gate, then we use just the || operator leaving unspecified the list 'list of gates'. In every case the processes must synchronise upon exiting.

14

It is also possible that in some cases more than two processes may synchronise at the same gate. For example, the expression:

causes gate a to be the synchronisation point of three different processes. All the three processes must offer an event at the same time. Otherwise the processes will be blocked. This means that if we had something like

$$(a; b; exit|[a]|a; d; exit)|[a]|b; a; exit$$

then we would be dealing with a deadlock situation.

#### 2.3.5 Hiding

Syntax: hide list of gates in B

A hide operator hides the gates listed in the 'list of gates' from external processes. If an action is not hidden, with respect to the environment, cooperation of the environment is required. By hiding an action we are able to make the synchronisation of two processes invisible and disable the use of the named gates by any other process.

#### 2.3.6 Successful termination: exit

The keyword **exit** indicates that a process has successfully terminated. This means that execution can continue to other processes as mentioned in the next section.

### 2.3.7 Enabling

Syntax:  $B_1 >> B_2$

The LOTOS enable operator has a similar function as the action prefix operator. It denotes that process  $B_2$  must start execution just after the successful termination of process  $B_1$ . It should be noted that  $B_1$  must terminate successfully (i.e through the **exit** operator) in order for  $B_2$  to start executing.

### 2.3.8 Disabling

Syntax:  $B_1 > B_2$

The LOTOS disable operator [> models an interruption of a process by another process. It means that in any point of the execution of  $B_1$ , process  $B_2$  can interrupt  $B_1$  and take over control. Once  $B_2$  starts executing the actions of the other process are no longer possible. On the other hand, if  $B_1$  terminates before  $B_2$  takes over control then  $B_2$  disappears.

#### 2.3.9 Process Instantiation

Syntax:  $B=P[g_1,...,g_n]$

By process instantiation, the behaviour of B becomes the behaviour of the process which is defined as P. The formal gates appearing in the definition of process P are substituted by the actual ones appearing in the expression above. We can define infinite behaviours in LOTOS by using recursive process instantiations.

### 2.4 Data Types

LOTOS data type part is based on the specification language for abstract types ACT-ONE. An abstract data type enables the user to specify his own data types and the corresponding operations on them, just as he is able to specify his own functions by the use of procedure declarations in conventional programming languages. The actions one must take, to define his own data types, are described below.

### 2.4.1 Signature

The first step in specifying a data type is to define its *signature*. Let's take a closer look at the example presented in Figure 2.

The *signature* of a data type defines its *sort* (type) and the operations permitted on this sort. *Sorts* can be viewed as named sets of elements. In our example

```

type Nat_Numbers is

sorts nat

opns 0:-> nat

succ: nat-> nat

endtype

domain

range

```

Figure 2: Example of a signature

we have defined a new type Nat\_numbers that is of sort nat and we have allowed two operations: The succ operation is performed on a data type of sort nat (the domain of the operation) and the result is another data type of the same sort (the range of the operation). The other operation is a nullary operation (constant) that results to a type of sort nat. Operations are functions that map a number of elements taken from a particular set (the domain) into a single element of another set, the range. We can construct all the elements of a sort if we know just one element of that sort by repeatedly applying a nullary operation to that element.

For example, we can view 0 as a term of type Nat\_numbers. A term is the result of applying an operation to other terms. For example some terms of the type Nat\_numbers are the following:

$$0$$

,  $succ(0)$ ,  $succ(succ(0))$ , ...

### 2.4.2 Equations

Equations provide us with means to prove the equivalence of two terms that belong to the same sort. *Equations* do not define new terms. They make our life easier by helping us to use simple terms that are equivalent with other more complex ones.

For example, if we add the following piece of code to the specification of the

signature of type Nat\_Numbers we will define an operation for addition.

eqns

forall x,y: nat

ofsort nat

$$x + 0 = x$$

$$x + succ(y) = succ(x+y)$$

Although we did not add any new terms to the set of  $Nat_Numbers$  we expressed a convenient method for defining members of this set. Instead of using the term succ(succ(0)) + succ(0) we can now equivalently use the term succ(succ(succ(0))).

Because this is a brief description of the language we will not expand further. We shall only outline some of the other features of LOTOS data types.

#### 2.4.3 Extension

After we have defined the signature of a type we can *extend* it by providing it with new operations, sorts and equations. This way the number of expressions derived from the data type is greatly enlarged.

### 2.4.4 Combining

Types can also be combined. Complex types can be easily constructed by using simpler ones. By combining sorts, operations and equations we obtain richer signatures that define more complex data structures.

### 2.4.5 Renaming

It is often the case that some data types are similar. Therefore, the renaming facility of LOTOS is used to generate a new independent type by changing the names of its components. Renaming is used every time we want to define a new type that has been used before, probably with another name.

#### 2.4.6 Parameterised Data Types

LOTOS data types are flexible enough to permit the reuse of signatures and operations. This is possible through the use of parameterisation. Parameterised data types look a lot like functions that can be called with certain parameters and perform a predefined set of operations on that parameters. They consist of a formal body with formal sorts and operations and a main body with its own sorts and operations much like a function's body. Each time a parameterised data type is called, its formal parameters are replaced by the parameters provided by the caller. A parameterised data type looks like:

```

formalsorts ...

formalopns ...

sorts ...

opns ...

eqns ....

```

### 2.5 Full LOTOS

Full LOTOS combines the power of basic LOTOS with the characteristics of abstract data types. In full LOTOS, it is possible to describe process synchronisation involving the exchange of data values. Thus, interprocess communication is available.

A specification written in full LOTOS is of the form:

```

specification spec_name[gate list](parameter list):functionality

type definitions

```

#### behaviour

behaviour expression

#### where

type definitions

process definitions

#### endspec

A process definition in full LOTOS has the form:

process proc\_name[gate list](parameter list):functionality:=

behaviour expression

#### where

type definitions process definitions

#### endproc

### 2.5.1 Action prefix

In full LOTOS an action is formed of three components:

- 1. A gate that denotes the place where the event is going to happen

- 2. A list of events.

- 3. An optional predicate

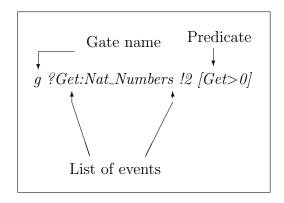

Consider the LOTOS expression presented in Figure 3. In this example we say that an event will occur at gate g. The variable Get will take an arbitrary value from the set of  $Nat_Numbers$  such that Get>0. We say that in this case we have a variable declaration and we can think that our process asks for a value

Figure 3: Actions in full LOTOS

to be offered (by some other process). After that, later instances of this variable expression will be replaced by this offered value. The other event is a *value declaration* and we can think of it as a value offer. In general we can think that the ? symbol indicates input, whereas the ! symbol indicates output.

### 2.5.2 Parallel Composition in Full LOTOS

The semantics of parallel composition do not change. The only constraints added are those that have to do with value offers.

Two processes can proceed in parallel if they offer the same value (value matching), or wait for an input of the same sort. In the latter, the same (random) value is assigned to both variables (value generation). If one process offers a value, while the other one is waiting for a value of that sort, then we actually have a message passing situation where one process takes the value offered by the other.

The reader can refer to other papers (e.g [ISO89a]) for a detailed description of the synchronisation conditions.

### 2.5.3 Successful termination with parameters

This is denoted by  $\mathbf{exit}(E_1,...,E_n)$ . The process that exits through this operator offers the values  $E_1,...,E_n$ . In order for two processes to be synchronised they

have to offer at the end the same set of values (in LOTOS terminology we say that they must have the same **functionality**).

#### 2.5.4 Guarded behaviour

A behaviour expression may also be preceded by some guard that must be true in order for the former to be enabled. For example, the expression:

$$[X < 2] - > g!X$$

;stop

will enable the offer of X only if its value is smaller than 2.

Guarded behaviours are extensively used in order to avoid specifications that lead to infinite execution trees.

#### 2.5.5 Sequential composition with value passing

In full LOTOS in order to connect two processes with the >> operator we have to use the following schema:

$$B_1 >>$$

accept  $X_1 : S_1, ..., X_n : S_n$  in  $B_2$

$B_1$ 's **functionality** must match with the sorts listed after the **accept** operator. If  $B_1$  exits then the next behaviour expression  $B_2$  becomes active and the variables  $X_1$  to  $X_n$  in  $B_2$  are substituted by the value results of  $B_1$  (i.e the **exit** parameters).

#### 2.5.6 Generalised choice

LOTOS provides us with a convenient way for expressing an infinite number of alternatives. The expression:

**choice**

$$x:Nat_Numbers[a;B(x)]$$

declares that x may be any of the natural numbers. After a choice from the set of natural numbers, the value of x will be placed in the expression B(x). The choice can be either non deterministic or it can be determined by the environment. We

can denote in a similar way a generalised choice over a set of gates. The expression has the following syntax:

**choice**

$$g$$

**in**  $[g_1,...,g_n][]B$

#### 2.5.7 Parametric processes

In full LOTOS we can parameterise process definitions by using variable declarations together with the list of formal gates. The syntax looks like the one in basic LOTOS:

**process** process\_name

$$[gate\_list](x_1:s_1,...,x_n:s_n)$$

:functionality := ... endproc

Whenever an expression of the form:

process\_name [actual gate parameters]

$$(v_1, ... v_n)$$

is met, process process\_name is instantiated and the formal parameters  $x_1, ..., x_n$  are replaced by the actual ones:  $v_1, ..., v_n$ .

#### 2.5.8 Local Definitions

We can replace a value identifier (i.e. a variable name) with a value expression by using the **let** construct of full LOTOS. The statement:

let

$$x_1 : Sort_1 = v_1, ..., x_n : Sort_n = v_n$$

in

will replace all occurrences of

$$x_1, ..., x_n$$

by the respective value expressions

$$v_1, ..., v_n$$

.

#### 2.5.9 Par Expression

Similar to the generalised choice expression is the **par** expression. Its syntax is:

par

$$g$$

in  $[g_1,...g_n]$  op  $B$

where op is any parallel operator. The expression is equivalent to

$$B[g/g_1]$$

op ... op  $B[g/g_n]$

where  $g/g_i$  means: replace g with  $g_i, i = 1, ..., n$

### 2.6 Epilogue

The above discussion about LOTOS (and especially the one referred to full LOTOS) is meant to be only a brief overview. The reader who wants to become familiar with the language is advised to read other tutorials, for example [JT93], [BB87] or [LFH92].

What the reader must have in mind, is that LOTOS gives us the ability to specify a system in various levels, from the highly abstract to the more detailed one. Through the years various techniques have been developed for specifying systems. Some are meant to ease the work of the implementer, others that of the specifier. Therefore, although LOTOS is an executable language, not all specifications may be able to produce running code. The problems of generating running code from LOTOS programs are discussed below.

## Chapter 3

## An overview of PROMELA

### 3.1 Prologue

PROMELA is a language for writing validation models. Its syntax is in many aspects a lot like C. The following is meant to be only a brief overview. The reader who wants a tutorial in PROMELA should consult reference [JH91].

#### 3.2 Statements

All the statements in PROMELA except the assignments and declaration of variables are conditionally executed i.e. statements are executed only when they can. For example, the boolean condition

$$a==b$$

is executed only when both a and b have the same value. Otherwise the statement is blocked. This is how PROMELA achieves synchronisation.

## 3.3 Variables, Data types

PROMELA supports the following data types:

bit, bool, byte, short, int, chan.

The first five types are basic data types, supported by almost any programming language. The data type *chan* is used to model message channels, enabling the transfer of data from one process to another.

PROMELA also supports the use of one dimensional arrays for all of the above data types.

### 3.4 Procedures

Procedures in PROMELA can be recursive, can accept parameters and return values to other procedures. Parameters are passed by value so the only way to return values from one procedure to another is to use global variables or message channels.

Each procedure in PROMELA can be viewed as a process. Therefore, as far as we are talking about PROMELA, we will use the terms procedure and process interchangeably. PROMELA uses the following syntax to define the name and the type of a procedure:

Statements are separated by the use of a semicolon ';' or an arrow '->'. The arrow is preferred to the semicolon in those occasions where the causal relation between two statements should be informally declared.

### 3.4.1 The initial process

In order to instantiate a process, the user has to explicitly execute it through the use of the *run* operator. The statement

will execute a process with the name process-name. The run statement is always executable, returns the pid of the process and it does not wait for the process to terminate. The first process to be executed is a special process named init that plays the same role as process main() in C.

#### 3.4.2 Atomic sequences

In PROMELA the user is also equipped with another useful command. The user may define that a sequence of statements should be executed as one, without any interleaving, by the use of the keyword *atomic*. Any number of statements included inside the atomic structure will be executed without any interruption from other processes. Attention must be paid to the fact that the user has to make sure that all the statements inside an atomic sequence are executable, and do not wait for a returned value from some other process. If this is the case, then the sequence will be blocked and the program will terminate abnormally.

### 3.5 Message channels

Message channels are data structures that provide a method for transferring data from one process to another.

By declaring that a variable is of type chan, e.g.

chan

$$a=[5]$$

of  $\{byte, int\}$

the user can use the variable 'a' to store up to 5 messages that consist of two fields: a byte and an integer field.

Any process that is inside the scope of variable 'a' can store a message, e.g.

stores a message consisting of the byte field c and the integer field 512, or, on the other hand, retrieve a message, e.g

#### a?var1,var2

Channels can be passed as parameters in procedure calls. They provide the means for communication between the callee and the caller. Whenever a message is placed in the channel, it is made available to all the processes that have access to that channel.

Channels pass messages in a first-in first-out order. The send operation is executable only when the channel addressed is not full, while the receive operation is only executable when the channel is non-empty. The user can set another condition on the executability of the receive operation by defining some of the fields as constants, in this way forcing the receive statement to execute only if these constants match the value of the corresponding field in the message that is at the head of the queue.

In order to avoid undesirable blocking, the user can test for the existence of messages before trying to collect them. For example, the statement:

is a boolean expression that returns true or false depending on whether or not the channel has that message at its head. However, the user must make certain that, in case the message exists, he will read the message before someone else catches it first. This can be ensured via the use of an atomic sequence.

Users can also use channels to achieve synchronous communication. This is achieved by declaring a message channel that can hold 0 messages, e.g.

This way the user actually defines a rendezvous port that can only pass and not store messages. Unfortunately, only two partners can be synchronised by this method. It will be shown later that this is a major drawback when it comes to the translation of LOTOS specifications.

### 3.6 Control Flow

PROMELA also provides the user with three different ways for defining control flow:

#### 1. Case Selection

For example, the user may write the following piece of code in order to demonstrate the possibility of a choice between two alternatives:

```

if

:: (a==true)-> <alternative1>

:: (a==false)-> <alternative2>

fi

```

The alternative statements are executed only if the first statements (which are called *guards*) are executable. If both of the *guards* are executable at the same time, the alternative statement to be executed is either of the two. The choice between the two is a non-deterministic one.

#### 2. Repetition

A similar structure can be used to model repetition. Instead of the **if/fi** pair the **do/od** is available in order to provide means for a loop. The program exits from the loop when a 'break' statement becomes executable. In the following example the program exits from the loop when the guard statement of break becomes executable, i.e when a==true.

```

do

:: (a==false)-> printf("Hello")

:: (a==true)-> break

od

```

#### 3. Jumps

They provide an alternative to the break statement. Instead of exiting a

loop through a *break* statement the user may define a jump to a predefined piece of code by the use of the **goto** command. Labels are used in order to define such pieces. In the following piece of code, the control will *jump* to the label *State\_1*: when boolean variable *a* becomes true:

#### 3.7 Timeouts

Timeouts are used to escape from hang states. Timeouts are extensively used in computer systems, e.g computer networks, and they prevent systems from hanging.

The timeout construct of PROMELA although does not use the notion of real time, characterises states where the control should be transferred in case no other transition is possible. The programmer can make sure that whenever a time-out statement becomes active, reset statements follow, together with appropriate warning messages to the user.

### 3.8 Correctness Criteria

In order to validate a design it is important to define what exactly is a "correct" design. A design can be proven to be correct only with respect to specific correctness criteria.

PROMELA provides us with a mechanism for defining that certain behaviours are impossible. Any protocol which violates any of the claims made by the above

mechanism is considered to be "incorrect". The following structures have been provided by PROMELA for defining impossible behaviours.

#### 3.8.1 Assertions

The PROMELA statement:

assert(cond)

is always executable and can be placed anywhere in a program. The above statement claims that the boolean condition 'cond' should never be true whenever the assert statement becomes executable. The user may also place assert statements in a special monitor() process, declaring that in any state of the program, 'cond' should never hold.

#### 3.8.2 Deadlocks

The user can also specify end states by placing an end-state label before any statement which may lead to the termination of the program. If the program terminates at any other statement then the termination is considered as an improper one, and the program is said to be deadlocked.

End-state labels are strings with the prefix end.

### 3.8.3 Non-progress cycles

In PROMELA we can also mark states that must be executed for the protocol to make progress by using the label *progress* or any other string that starts with that word. If the protocol makes infinite cycles through states that do not make progress, then the protocol is considered to be incorrect.

#### 3.8.4 Livelocks

PROMELA has the ability to claim that something cannot happen infinitely often. By preceding an acceptance-state label before some statement we claim that this statement may not be part of a sequence of statements that can be repeated an infinite number of times. A program that cycles through the same series of states infinitely, is said to be *livelocked*.

Any label starting with the string accept is an acceptance-state label.

### 3.8.5 Temporal claims

The last and most powerful mechanism that PROMELA provides for the check of the validation of a system is that of temporal claims. The PROMELA notation for a temporal claim is:

```

never { ... }

```

A temporal claim defines an order of statements that is impossible to occur. By the term *order of statements* we mean the sequential order where each statement is executed *immediately* after the other (and not just *eventually after*).

The claim is usually a finite state machine. Whenever an undesirable behaviour has occured, the automaton reaches its end (acceptance) state where it cycles infinitely. For example:

```

never {

do

:: !flag-> skip

:: flag->

accept_label:

skip

od;

}

```

is an automaton that reaches its acceptance state whenever variable flag becomes true. The claim says that it is an error for that variable to become true.

Temporal claims combined with assertions, progress-state labels or acceptance state labels enable us to catch more types of errors. However, temporal claims increase enormously the complexity of validation programs and therefore they are rarely used.

# 3.9 A simple example

In chapter 1 (section 1.4) it was stated that: "In order for the verification procedure to understand and analyse a specification, both the protocol and its properties have to be written in some predefined notation".

In this application, this predefined notation is PROMELA.

PROMELA is the language that SPIN (the validation tool used in this project) understands. It can be used to express both the specification and the properties of a protocol. An example of this is presented below:

Suppose we want to specify a buffer that can hold up to k elements. One way to do this is to specify k interconnected buffers that can hold up to 1 element each [Mil89]. We can specify that in PROMELA as follows (k = 2 in this paradigm):

The specification for the one element buffer will look like:

```

proctype buffer(chan in,out)

{

int value;

do

::in?value;

out!value

od

}

```

The buffer just copies elements from its input to its output.

But we want to create a buffer that can hold more than one element. To do that all we have to do is to connect the output of one buffer to the input of the other. For a two element buffer we should then have:

This concludes the specification of a two place buffer.

Finally, following LOTOS ideas, an extra process that plays the role of the environment feeding the buffer with elements and taking the elements the buffer outputs could be added. In this case the elements could be numbers. If we feed the buffer with a number, then we increase by one the number we 'll put in next time. If we take something out of the buffer then we decrease the number we input by one. So the specification of the environment will look like:

```

proctype environment(chan in,out)

{

int value;

value=1;

do

::in!value;

value=value+1

::out?value;value=value-1

od

}

```

Furthermore, we should add a line that initiates the environment process before anything else. So, the *atomic* statement in the **init** process will look like:

```

atomic {

run environment(in,out);

run buffer(in,hide);

run buffer(hide,out)

}

```

But, is the specification correct? To prove that the specification is correct all we have to do is to prove that the environment never inputs a number that is greater than 2, because that would mean that it would input more than two numbers without taking out any. In other words, that would mean that the buffer can hold more than two elements. In PROMELA the proof is easy. All that has to be done is the addition of an assert statement that checks that the numbers the environment inputs are indeed not greater than 2, in any case. So, the specification of the environment together with the specification of the properties we want to check is:

```

proctype environment(chan in,out)

{

int value;

value=0;

do

::in!value;

assert(value<3);

value=value+1

::out?value;value=value-1

od

}</pre>

```

Thus, it has been shown how PROMELA can be used to specify both a protocol and its expected behaviour. Other constructs could be used to prove that the buffer eventually inputs a number greater than 0.

# 3.10 Epilogue

Although we did not mention all the facilities of PROMELA e.g macro definitions, we made clear that it is a powerful validation language.

Designers can fairly easily write any protocol they want to verify and properties the protocol must have. Of course, one must bear in mind when writing that not all the protocols and their properties can be effectively verified, no matter what the language constructs are.

# Chapter 4

# An overview of SPIN

# 4.1 Prologue

Protocol verification plays a crucial role in protocol design. Even the most carefully developed protocol specifications may contain errors that will only be detected after exhaustive analysis. The role of a validator is to carry out this analysis and intelligently detect and report any pitfalls the specification may have.

During the years, a lot of automated methods for verification have been developed. SPIN is one such validator that encapsulates most of the available algorithms for protocol verification. It accepts as input a specification written in PROMELA, performs some analysis on this specification and reports any errors. The algorithms and the way SPIN works will be explained below.

## 4.2 Validation algorithms

SPIN's validation algorithms are based on reachability analysis. SPIN tries to analyse all the possible execution sequences starting from a given initial state.

Reachability analysis algorithms can be categorised into three main types:

- Full state search

This method works well for specifications which are not likely to produce more than 100,000 states.

#### - (Controlled) Partial search

The method is intended for larger systems, that can not be handled by the full state search algorithm. However, this technique has an upper limit and does not work for systems with more than 100,000,000 states.

#### - Random execution

This technique is used when both of the previous methods have failed. It is intended for huge systems whose state space is too large to be explored.

The performance of a reachability analysis algorithm is measured according to its *coverage* and its *quality*. These quantities are defined as follows:

$$coverage = \frac{states\ searched}{actual\ number\ of\ states}$$

$$quality = \frac{errors\ found}{actual\ number\ of\ errors}$$

#### 4.2.1 Full State Search Method

The algorithm tries to detect which states of the system are reachable and which are not. Unreachable states are pieces of un-executable code in the specification, or error states. Then it tries to analyse all the possible execution sequences.

Any executable sequence of reachable states must be free of deadlocks, of livelocks or of any other criteria the user has imposed.

The obvious problem of the full search method is that it performs well only if the number of states produced by the analysis of the specification is smaller than the number of states the system can store. Moreover, when the number of states produced exceeds the memory capacity of the system the *quality* of the full search method tends to decrease dramatically, together with the *coverage*.

Unfortunately, most of the working protocols today, generate a state space that is too large for exhaustive analysis. Therefore, the full state search algorithm can be used only for relatively small specifications.

#### 4.2.2 Controlled partial search

The controlled partial search method is based on the fact that in most cases it is impossible to fully search the state space produced by a specification. The central idea is that we can pay off this drawback of low *coverage* by maximising the *quality* of the search.

Controlled partial search analyses a number K of states while it makes sure that this number is much smaller than the actual number of states produced.

This can be achieved by many different techniques. There are algorithms that put an upper limit to the length of the execution sequences they analyse (*Depth Bound*). Others try to 'guess' which execution sequences may lead to deadlocks and they analyse only these sequences (*Scatter Search*). Some algorithms analyse the execution sequences that are more likely to happen (*Probabilistic Search*) while others try to drop sequences that are not relevant in the search for error states (*Partial Orders*). Finally, efforts are made to develop algorithms that proceed to the validation of an execution sequence according to some cost function that calculate based upon the states of the sequence (*Guided Search*).

SPIN uses another technique based on random selections of execution sequences. The algorithm promises to be more effective than the ones mentioned above and it guarantees that the quality of the search will be the maximum possible. This algorithm, called the super trace algorithm tries to organise a memory by using all the available bytes and performing the largest search possible. To determine whether a state s is a member of set A the method uses a hash table where it stores information on whether a certain state s has been processed or not. It minimises the amount of memory used, by using a hash table with a very large number of buckets  $(10^8)$ . Thus, it is possible in most cases to determine a state

if you know the bucket it lies in. This fact decreases the amount of information needed for describing a state linked with a certain bucket and therefore reduces the amount of memory the validator uses. For a discussion on this method the reader can refer to reference [JH91].

#### 4.2.3 Random simulation

The method is used for huge systems, where the state space may be over 10<sup>8</sup> states. The technique will work even for an *infinite* number of states. The state space is explored by a random walk over the transitions of the system. The user can try the algorithm for more than one time, collecting this way more data for his specification.

Although the coverage of the method is low, it has been proven by Colin West that the quality can be, in some cases, adequate [JH91].

## 4.3 Other algorithms

The algorithms explained so far are used by SPIN to decide which execution sequences should be checked and which assertions have been violated. For the detection of other errors in these sequences SPIN uses a number of different techniques.

To detect the presence of non progress and acceptance cycles and temporal claims SPIN uses the following algorithms.

Detection of non progress cycles

The algorithm for the detection of non progress cycles used by SPIN performs a depth first reachability analysis. When a progress state is reached the search stops. If during the process a cycle is detected then this means that it is a non-progress cycle.

Of course there is a possibility that a non-progress cycle appears after a progress cycle has been seen. To take care of this case SPIN creates another state space that consists of the original one but where transitions from progress states are disabled. The algorithm checks if it can create a cycle by combining every possible prefix of a cyclic sequence of the initial space with the ones in the second state space.

#### Detection of acceptance cycles

The algorithm used by SPIN is actually the one presented in [CVY90]. According to [CVY90, JH91] the algorithm uses the depth-first algorithm to traverse two state spaces (that they are initially the same). Let the two state spaces be named A and C respectively. Then for every acceptance state removed from the work space W and added to set A the algorithm swaps A and C and starts searching again. If during this search, the same acceptance state (called the seed state) is revisited then an acceptance cycle has been found. If the seed state is not visited again then the second search terminates when all the successors of the seed state have been added to C. Then the algorithm starts again using set A this time.

For a detailed description of the algorithm as well as a proof that this algorithm finds indeed all the acceptance cycles the reader should refer to [CVY90].

#### Temporal Claims

Temporal claims are usually easy to check. A temporal claim, as mentioned in the previous chapter, is actually a finite state machine. So, to check a termoral claim, all we have to do is to try to match every transition of the automaton that represents the claim with a transition in the state space.

#### The algorithm goes as follows:

For every new state the search enters, we try to make a transition in the finite state machine that represents the temporal claim. If the transition can not be made then the search is truncated as in the case where a state match occurs. If no transition from the initial state space can be matched

by a a transition in the finite state machine of the claim, then the behaviour the claim represents is impossible.

# 4.4 Using the validator

The validator can be used to make either a random simulation, or an exhaustive search or a controlled partial search.

For a random search, a statement of the form:

where a specification file is a specification written in PROMELA, will produce after a while a compact report on the number of process created, the states (if any) where the process has been blocked and other useful information. Different parameters given in the command line will generate more information.

If we want to produce an analyser for an exhaustive or a partial search the validator has to be called as follows:

This will produce a file named *pan.c* that contains the analyser for the specification. This is a program written in C and must be compiled in order to produce executable code.

The compilation flags determine the type of the search (exhaustive or partial) the analyser will make. A compilation without any flags, e.g:

produces an exhaustive search analyser, while on the other hand a *-DBITSTATE* option produces an analyser that performs a controlled partial search. The user can also define upper limits for the memory used, the maximum search depths and other useful parameters.

As soon as the analyser has completed execution and independently of the search method followed, it will report whether it has found any errors, the number of states searched and the total number of states together with some other information.

In the event of an error, a file called *pan.trail* is produced with the sequence of the steps that leaded to it. The user can follow this sequence by instructing *spin* to follow the trail written in *pan.trail*, using the command line option of *spin*: -t.

# 4.5 Validation Techniques

Although controlled partial search can handle systems with up to 10<sup>8</sup> states, most of the time this is not enough. Protocols of realistic complexity produce a number of states that is some magnitudes larger than 10<sup>8</sup>. Therefore, it is necessary that protocols are written in such a way that the validation will be the easiest possible.

One method is to define a protocol in different levels and try to validate each level at a time. Protocols may have parts that are completely independent from one another, so a validation made in different stages with each stage handling just one part of the specification is possible.

The same technique can be used if we specify a protocol step by step verifying each time a different property of it.

For example a verifier for all the three lowest level of the OSI architecture would have to explore some billions of states. But the case is simpler if we try to validate a level at a time, and then, assuming that the protocols describing the internal functions of the three levels work properly, try to verify that the protocol for the interactions among them works with no errors.

In addition, the specifier must try to minimise the number of different execution sequences of the system. Usage of *atomic sequences* tends to decrease the interleaving factor, leading to a smaller number of different states the analyser has to explore.

# 4.6 Epilogue

Although the progress made in the area of verification the last years is great, the problem of verifying large protocols is still open.

It is proven that the problem of analysing the state space produced by a specification is a *PSPACE* problem. Efforts have been made to obtain algorithms that can be applied to a large class of problems, but so far the range of realistic protocols that can be verified remains rather small.

# Chapter 5

# Translation of basic LOTOS

# 5.1 Prologue

In this chapter, the process of generating extended finite state machines (XFSMs) from basic LOTOS specifications will be described. The protocol which specifies the way XFSMs are synchronised with each other will be explained in subsequent chapters.

The work is based mainly on two papers. In cite [Kar92] a method is described for deriving extended finite state machines for full LOTOS specifications. A similar work is presented in reference [VSC90], but the execution model is somewhat different. An intermediate model for LOTOS specifications is also presented in cite [AMnS92].

The execution model we have followed is closer to that of reference [VSC90] although some ideas have been taken from reference [Kar92] as well.

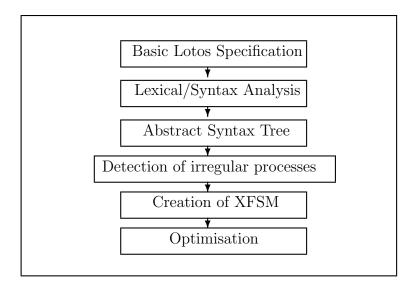

The first section of the chapter briefly describes the lexical and syntax analysis phase of the translator. After the syntax analysis phase, abstract syntax trees are created. This process is described in the third section of the chapter. Section four provides details on the method irregular process are identified. The procedure for generating extended finite state machines from abstract syntax trees is described in the fifth section. Finally, the last part has information on the method followed

Figure 4: Path to implement the translator

for the optimisation of the finite state machines produced.

In Figure 4 the path followed to produce finite automata from LOTOS specifications is shown.

# 5.2 Lexical and Syntax Analysis

The tools used for the lexical and syntax analysis phase of the translator are the widely known programs Lex [ELS75] and Yacc [CJ78].

#### • Lexical Analysis

The translator accepts as input any basic LOTOS expressions, as presented in cite [BB87]. Anything inside (\* ... \*) is considered to be a comment and therefore is disregarded.

#### • Syntax Analysis

The syntax analysis will efficiently parse basic LOTOS specifications with only one exception. Procedures must not be nested. The unfolding of nested procedures can be done through a special 'pre-compiler' process that is described in reference [ISO89a].

The process is called *flattening* of a specification and it is intended for full LOTOS. However, it can be applied to basic LOTOS as well. Among the main functions of this procedure is the renaming of identifiers (so that each one will become unique), the separation of the data from the control part and the unfolding of nested procedures.

So the translator's input may be specifications that look like:

```

specification spec_name [gate list] :functionality

behaviour

behaviour expression

where

process definition

...

process definition

endspec

```

A process definition looks like:

```

process proc_name [gate list] :functionality:=

behaviour expression

endproc

```

The context free grammar used in the syntax analysis phase is based on the one presented in [ISO89a]. The difference is that, since the parser is intended for basic LOTOS, any production containing data types has been removed. The grammar can be found in Appendix A.

#### • Symbol Table

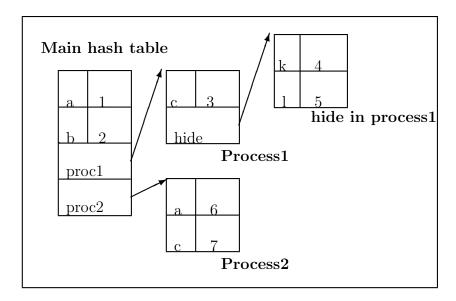

The symbol table that holds information about the identifiers used in a specification (such as gate and process identifiers) is a hash table that consists of other hash tables [PPP91].

Each process has its own table. Identifiers declared in the specification body can be found in the root table. In addition, each time a **hide** operator is met, a new child hash table is generated. This way scope information is easily represented. The identifiers a behaviour expression can access are the ones declared in the current and the 'father' hash tables. Although scope rules in basic LOTOS are not so complex, the symbol table was designed to handle full LOTOS specifications. In Figure 5, an example on the way information is represented in the symbol table is shown. The example illustrates the state of the symbol table after a specification of the form:

has been analysed.

Furthermore, to make sure that gates and processes have unique names, a unique number is assigned to each gate and process every time a new

Figure 5: Structure of the symbol table

identifier is declared. Therefore, after the syntax analysis, each gate consists of a name (its lexeme) and a number. It is likely that the code generated from the LOTOS specification will sometimes refer to a gate by its number and not by its name.

## 5.3 Creation of Abstract Syntax Trees

An abstract syntax tree for the specification being analysed is constructed during the syntax analysis phase of the translator.

Abstract syntax trees can be thought as parse trees where each node reflects to an operator [VASDU86]. The branches of a node point to its operands. Abstract syntax trees provide us with an intermediate representation that allow one to further process and transform the input text.

In LOTOS case, we do not maintain just one single abstract syntax tree but a forest of abstract syntax trees. Each tree in the forest represents a process definition in the LOTOS specification.

Trees may point to each other. This is the case when a process instantiation

occurs. A node that represents process instantiation points to the root of the tree that represents the process that is about to be instantiated. This leads us to the creation of a directed acyclic graph (dag).